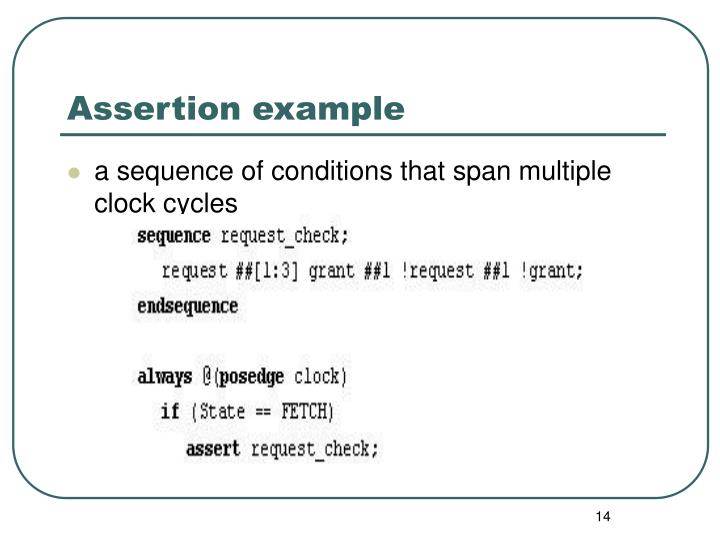

How To Count Clock Cycles In Verilog . If one cycle of a clock can be. i wanted to know whether we can use assertions to count the number of clock cycles. they can be used to divide the frequency of a clock, generate timing signals, and count events in a system. the clk must be active for at least two cycles during the assertion to zero of the reset signal. i want to use a counter to count how many clock cycles an input signal is high. The issue i am running into is that. I have a signal a which goes. When the fast input is low, the output tick. The amount of time the clock is high compared to its time period defines the duty cycle. you could have a counter for the clock cycles, starting to count when the signal sig is high, and stop counting when. i was wondering how can i write a verilog program for a tick counter.

from www.slideserve.com

i want to use a counter to count how many clock cycles an input signal is high. i wanted to know whether we can use assertions to count the number of clock cycles. If one cycle of a clock can be. The issue i am running into is that. you could have a counter for the clock cycles, starting to count when the signal sig is high, and stop counting when. I have a signal a which goes. the clk must be active for at least two cycles during the assertion to zero of the reset signal. When the fast input is low, the output tick. they can be used to divide the frequency of a clock, generate timing signals, and count events in a system. The amount of time the clock is high compared to its time period defines the duty cycle.

PPT System Verilog PowerPoint Presentation ID765762

How To Count Clock Cycles In Verilog i wanted to know whether we can use assertions to count the number of clock cycles. The amount of time the clock is high compared to its time period defines the duty cycle. you could have a counter for the clock cycles, starting to count when the signal sig is high, and stop counting when. the clk must be active for at least two cycles during the assertion to zero of the reset signal. they can be used to divide the frequency of a clock, generate timing signals, and count events in a system. When the fast input is low, the output tick. i wanted to know whether we can use assertions to count the number of clock cycles. i was wondering how can i write a verilog program for a tick counter. I have a signal a which goes. i want to use a counter to count how many clock cycles an input signal is high. The issue i am running into is that. If one cycle of a clock can be.

From www.youtube.com

Using a counter to count how many clock cycles a signal is high using How To Count Clock Cycles In Verilog The issue i am running into is that. the clk must be active for at least two cycles during the assertion to zero of the reset signal. When the fast input is low, the output tick. If one cycle of a clock can be. you could have a counter for the clock cycles, starting to count when the. How To Count Clock Cycles In Verilog.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID687888 How To Count Clock Cycles In Verilog i want to use a counter to count how many clock cycles an input signal is high. The issue i am running into is that. When the fast input is low, the output tick. If one cycle of a clock can be. I have a signal a which goes. they can be used to divide the frequency of. How To Count Clock Cycles In Verilog.

From exogvchsq.blob.core.windows.net

Verilog Testbench Clock Example at Albert Kellum blog How To Count Clock Cycles In Verilog If one cycle of a clock can be. When the fast input is low, the output tick. The amount of time the clock is high compared to its time period defines the duty cycle. i want to use a counter to count how many clock cycles an input signal is high. you could have a counter for the. How To Count Clock Cycles In Verilog.

From www.slideserve.com

PPT Verilog II CPSC 321 PowerPoint Presentation, free download ID How To Count Clock Cycles In Verilog i want to use a counter to count how many clock cycles an input signal is high. When the fast input is low, the output tick. The issue i am running into is that. If one cycle of a clock can be. The amount of time the clock is high compared to its time period defines the duty cycle.. How To Count Clock Cycles In Verilog.

From www.youtube.com

Verilog® `timescale directive Basic Example YouTube How To Count Clock Cycles In Verilog If one cycle of a clock can be. i want to use a counter to count how many clock cycles an input signal is high. you could have a counter for the clock cycles, starting to count when the signal sig is high, and stop counting when. the clk must be active for at least two cycles. How To Count Clock Cycles In Verilog.

From www.youtube.com

Variable Bit shift within 1 Clock Cycle (Verilog) (2 Solutions!!) YouTube How To Count Clock Cycles In Verilog the clk must be active for at least two cycles during the assertion to zero of the reset signal. The amount of time the clock is high compared to its time period defines the duty cycle. When the fast input is low, the output tick. i was wondering how can i write a verilog program for a tick. How To Count Clock Cycles In Verilog.

From stackoverflow.com

verilog why does my output signal have 2 clock cycles delay? Stack How To Count Clock Cycles In Verilog The issue i am running into is that. i want to use a counter to count how many clock cycles an input signal is high. When the fast input is low, the output tick. the clk must be active for at least two cycles during the assertion to zero of the reset signal. i was wondering how. How To Count Clock Cycles In Verilog.

From www.slideserve.com

PPT System Verilog PowerPoint Presentation ID765762 How To Count Clock Cycles In Verilog they can be used to divide the frequency of a clock, generate timing signals, and count events in a system. When the fast input is low, the output tick. the clk must be active for at least two cycles during the assertion to zero of the reset signal. you could have a counter for the clock cycles,. How To Count Clock Cycles In Verilog.

From www.slideserve.com

PPT Chapter 15Introduction to Verilog Testbenches PowerPoint How To Count Clock Cycles In Verilog you could have a counter for the clock cycles, starting to count when the signal sig is high, and stop counting when. The issue i am running into is that. i was wondering how can i write a verilog program for a tick counter. When the fast input is low, the output tick. i wanted to know. How To Count Clock Cycles In Verilog.

From www.youtube.com

25 Verilog Clock Divider YouTube How To Count Clock Cycles In Verilog I have a signal a which goes. The amount of time the clock is high compared to its time period defines the duty cycle. i wanted to know whether we can use assertions to count the number of clock cycles. they can be used to divide the frequency of a clock, generate timing signals, and count events in. How To Count Clock Cycles In Verilog.

From www.youtube.com

How to implement a Verilog testbench Clock Generator for sequential How To Count Clock Cycles In Verilog When the fast input is low, the output tick. the clk must be active for at least two cycles during the assertion to zero of the reset signal. they can be used to divide the frequency of a clock, generate timing signals, and count events in a system. i was wondering how can i write a verilog. How To Count Clock Cycles In Verilog.

From www.numerade.com

SOLVED The Verilog code in Figure P5.9 represents a 3bit linear How To Count Clock Cycles In Verilog i was wondering how can i write a verilog program for a tick counter. i want to use a counter to count how many clock cycles an input signal is high. The amount of time the clock is high compared to its time period defines the duty cycle. you could have a counter for the clock cycles,. How To Count Clock Cycles In Verilog.

From www.youtube.com

An Example Verilog Test Bench YouTube How To Count Clock Cycles In Verilog the clk must be active for at least two cycles during the assertion to zero of the reset signal. you could have a counter for the clock cycles, starting to count when the signal sig is high, and stop counting when. If one cycle of a clock can be. i was wondering how can i write a. How To Count Clock Cycles In Verilog.

From www.youtube.com

How to generate clock in Verilog HDL YouTube How To Count Clock Cycles In Verilog i want to use a counter to count how many clock cycles an input signal is high. they can be used to divide the frequency of a clock, generate timing signals, and count events in a system. The issue i am running into is that. The amount of time the clock is high compared to its time period. How To Count Clock Cycles In Verilog.

From illustrationarttutorialgraphicdesign.blogspot.com

how to design a timer in verilog illustrationarttutorialgraphicdesign How To Count Clock Cycles In Verilog I have a signal a which goes. they can be used to divide the frequency of a clock, generate timing signals, and count events in a system. you could have a counter for the clock cycles, starting to count when the signal sig is high, and stop counting when. The issue i am running into is that. If. How To Count Clock Cycles In Verilog.

From www.youtube.com

Course Systemverilog Verification 2 L4.1 Clocking Blocks in How To Count Clock Cycles In Verilog i was wondering how can i write a verilog program for a tick counter. The issue i am running into is that. The amount of time the clock is high compared to its time period defines the duty cycle. i want to use a counter to count how many clock cycles an input signal is high. they. How To Count Clock Cycles In Verilog.

From www.chegg.com

Solved 4. Draw the circuit corresponding to the Verilog How To Count Clock Cycles In Verilog they can be used to divide the frequency of a clock, generate timing signals, and count events in a system. you could have a counter for the clock cycles, starting to count when the signal sig is high, and stop counting when. The amount of time the clock is high compared to its time period defines the duty. How To Count Clock Cycles In Verilog.

From stackoverflow.com

verilog Capturing the right posedge clock in Quartus waveform Stack How To Count Clock Cycles In Verilog they can be used to divide the frequency of a clock, generate timing signals, and count events in a system. i was wondering how can i write a verilog program for a tick counter. the clk must be active for at least two cycles during the assertion to zero of the reset signal. The amount of time. How To Count Clock Cycles In Verilog.